- 您现在的位置:买卖IC网 > Sheet目录251 > SFCF64GBH2BU4TO-I-NU-517-STD (Swissbit NA Inc)FLASH SLC UDMA/MDMA/PIO 64GB

j)

k)

l)

m)

n)

o)

p)

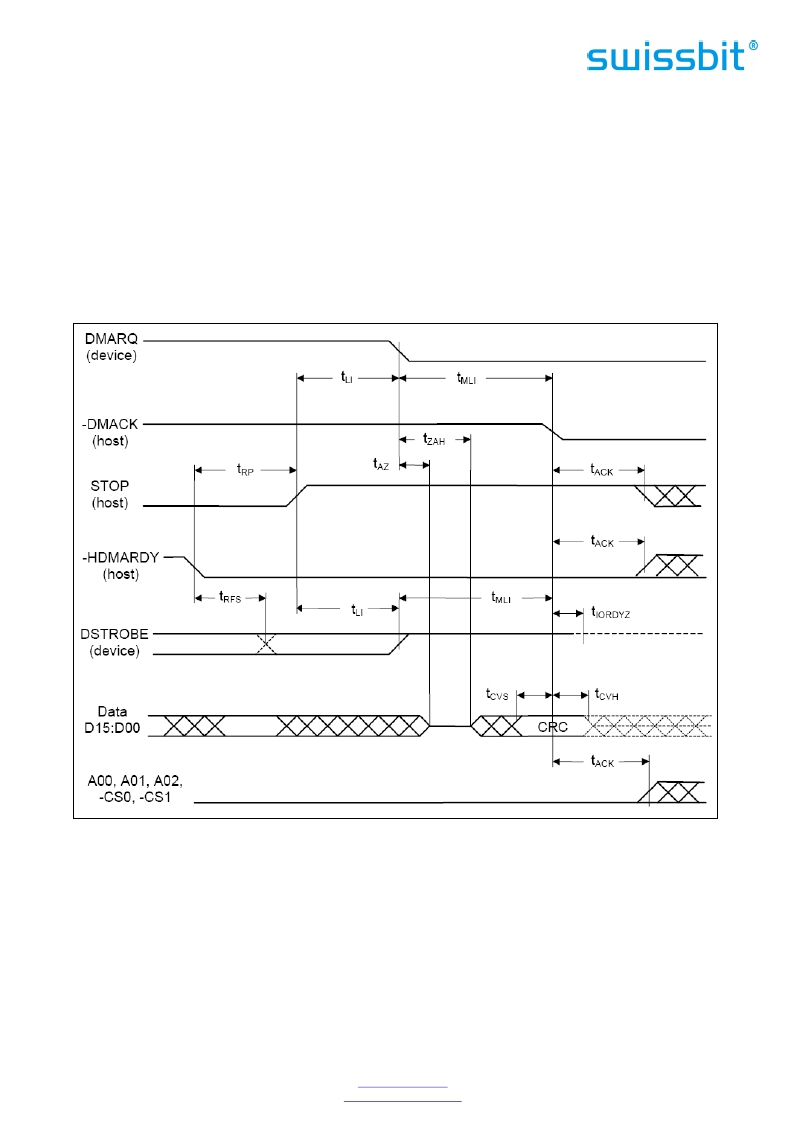

If the host has not placed the result of its CRC calculation on D[15:0] since first driving D[15:0] during (9),

the host shall place the result of its CRC calculation on D[15:0] (see 6.5.4.5 ).

The host shall negate – DMACK no sooner than t MLI after the device has asserted DSTROBE and negated

DMARQ and the host has asserted STOP and negated – HDMARDY, and no sooner than t DVS after the host

places the result of its CRC calculation on D[15:0].

The device shall latch the host’s CRC data from D[15:0] on the negating edge of – DMACK.

The device shall compare the CRC data received from the host with the results of its own CRC calculation. If

a miscompare error occurs during one or more Ultra DMA burst for any one command, at the end of the

command, the device shall report the first error that occurred (see 6.5.4.5 ).

The device shall release DSTROBE within t IORDYZ after the host negates – DMACK.

The host shall neither negate STOP nor assert – HDMARDY until at least t ACK after the host has negated –

DMACK.

The host shall not assert – IORD, -CS0, -CS1, A2, A1, or A0 until at least t ACK after negating DMACK.

Figure 14: Ultra DMA Data-In Burst Host Termination Timing

Notes: The definitions for the STOP, HDMARDY, and DSTROBE signal lines are no longer in effect after

DMARQ and DMACK are negated.

6.5.4.4.6 Initiating an Ultra DMA Data-Out Burst

An Ultra DMA Data-out burst is initiated by following the steps lettered below. The timing diagram

is shown in Figure 15: Ultra DMA Data-Out Burst Initiation Timing. The timing parameters are

specified in Table 26: Ultra DMA Data Burst Timing Requirements and are described in Table 27: Ultra DMA Data

The following steps shall occur in the order they are listed unless otherwise specifically allowed:

a) The host shall keep – DMACK in the negated state before an Ultra DMA burst is initiated.

b) The device shall assert DMARQ to initiate an Ultra DMA burst.

c)

Steps I, (d), and (e) may occur in any order or at the same time. The host shall assert STOP.

d) The host shall assert HSTROBE.

Swissbit AG

Industriestrasse 4

Swissbit reserves the right to change products or specifications without notice.

Revision: 1.00

CH-9552 Bronschhofen

Switzerland

www.swissbit.com

industrial@swissbit.com

C-440_data_sheet_CF-HxBU_Rev100.doc

Page 35 of 102

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

SFN08B4702CBQLF7

RES ARRAY 47K OHM 7 RES 8-DFN

SFP1050-12BG

FRONT END AC/DC 1050W 12V

SFP450-12BG

PWR SUP 450W 12V 36.6A W/STANDBY

SFSD1024N1BN1TO-I-DF-151-STD

FLASH MICRO SD CARD IND S-200 1G

SFSD2048L1BN2TO-I-DF-151-STD

FLASH SECURE DGTL CARD SD 2G

SFSD4096L1BN2TO-I-Q2-141-STD

FLASH SECURE DGTL CARD SDHC 4G

SFSD8192N1BW1MT-E-QG-111-STD

FLASH MICRO SD 8GB EXT TEMP

SFUI4096J1BP2TO-I-DT-211-STD

FLASH DRIVE USB MODULE U-110 4G

相关代理商/技术参数

SFCF64GBH2BU4TO-I-NU-527-STD

制造商:SWISSBIT 功能描述:CFC C-440 DENSITY INDUSTRIAL - Trays 制造商:SWISSBIT NA INC 功能描述:FLASH CARD 64GB IND C-440 制造商:Swissbit 功能描述:Memory Cards 64GB IND COMPACT FLASH SLC NAND C440

SFCF8192H1BO2TO-C-Q1-523-SMA

制造商:SWISSBIT NA INC 功能描述:FLASH

SFCF8192H1BO2TO-C-Q1-533-ZP1

制造商:SWISSBIT NA INC 功能描述:FLASH

SFCF8192H1BO2TO-C-Q1-543-SMA

制造商:SWISSBIT NA INC 功能描述:FLASH

SFCF8192H1BO2TOIQ1523SMA

制造商:Swissbit 功能描述:Flash Card 8G-Byte 3.3V/5V CompactFlash 50-Pin

SFCF8192H1BO2TO-I-Q1-523-SMA

功能描述:FLASH SLC UDMA/MDMA/PIO 8G RoHS:是 类别:存储卡,模块 >> 存储器,PC 卡 系列:C-320 标准包装:30 系列:- 存储容量:8GB 存储器类型:存储卡 - Extreme III SD?

SFCF8192H1BO2TO-I-Q1-533-ZP1

制造商:SWISSBIT NA INC 功能描述:FLASH

SFCF8192H1BO2TO-I-Q1-543-SMA

制造商:SWISSBIT NA INC 功能描述:FLASH